## **PSRAM**

# 2-Mbit (128K x 16)

# Pseudo Static RAM

### **Features**

Wide voltage range: 2.7V–3.6V

Access Time: 55 ns, 70 ns

· Ultra-low active power

- Typical active current: 1mA @ f = 1 MHz

— Typical active current: 14 mA @ f = fmax (For 55-ns)

—Typical active current: 8 mA @ f = fmax (For 70-ns)

· Ultra low standby power

Automatic power-down when deselected

CMOS for optimum speed/power

### **Functional Description**

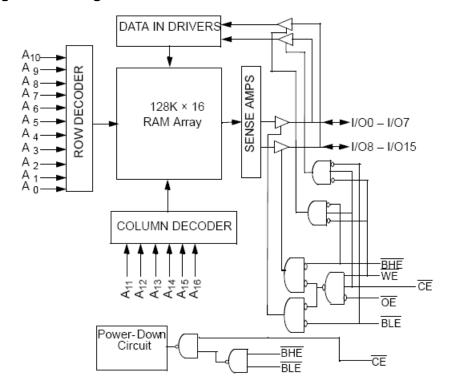

The M24L216128SA is a high-performance CMOS Pseudo Static RAM organized as 128K words by 16 bits that supports an asynchronous memory interface. This device features advanced circuit design to provide ultra-low active current. This is ideal for portable applications such as cellular telephones. The device can be put into standby mode when deselected ( $\overline{\text{CE}}$  HIGH or both  $\overline{\text{BHE}}$  and  $\overline{\text{BLE}}$  are HIGH). The input/output pins (I/O<sub>0</sub> through I/O<sub>15</sub>) are placed in a high-impedance state when the chip is deselected ( $\overline{\text{CE}}$  HIGH), or when the outputs are disabled ( $\overline{\text{OE}}$  HIGH), or

when both Byte High Enable and Byte Low Enable are disabled ( $\overline{BHE}$ ,  $\overline{BLE}$  HIGH), or during a write operation ( $\overline{CE}$  LOW and  $\overline{WE}$  LOW).

Writing to the device is accomplished by asserting Chip Enable ( $\overline{\text{CE}}$  LOW) and Write Enable ( $\overline{\text{WE}}$ ) input LOW. If Byte Low Enable ( $\overline{\text{BLE}}$ ) is LOW, then data from I/O pins (I/O<sub>0</sub> through I/O<sub>7</sub>), is written into the location specified on the address pins (A<sub>0</sub> through A<sub>16</sub>). If Byte High Enable ( $\overline{\text{BHE}}$ ) is LOW, then data from I/O pins (I/O<sub>8</sub> through I/O<sub>15</sub>) is written into the location specified on the address pins (A<sub>0</sub> through

$A_{16}$ ).

Reading from the device is accomplished by asserting Chip Enable ( $\overline{\text{CE}}$  LOW) and Output Enable ( $\overline{\text{OE}}$ ) LOW while forcing the Write Enable ( $\overline{\text{WE}}$ ) HIGH. If Byte Low Enable ( $\overline{\text{BLE}}$ ) is LOW, then data from the memory location specified by the address pins will appear on I/O<sub>0</sub> to I/O<sub>7</sub>. If Byte High Enable( $\overline{\text{BHE}}$ ) is LOW, then data from memory will appear on I/O<sub>8</sub> to I/O<sub>15</sub>. Refer to the truth table for a complete description of read and write modes.

## **Logic Block Diagram**

Publication Date: Jul. 2008 Revision: 1.2 1/14

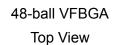

## Pin Configuration[2, 3, 4]

44-pin TSOPII Top View

## **Product Portfolio Product**

|                |                           |      |      |           |                                |                   | Power D | Dissipatio                    | n        |      |

|----------------|---------------------------|------|------|-----------|--------------------------------|-------------------|---------|-------------------------------|----------|------|

| Product        | V <sub>CC</sub> Range (V) |      |      | Speed(ne) | Operating I <sub>CC</sub> (mA) |                   |         | Standby long(uA)              |          |      |

| Product        |                           |      |      | Speed(ns) | f = 1N                         | f = 1MHz f = fmax |         | Standby I <sub>SB2</sub> (µA) |          |      |

|                | Min.                      | Тур. | Max. |           | Typ.[5]                        | Max.              | Typ.[5] | Max.                          | Typ. [5] | Max. |

| M24L216128SA   | 55                        |      | 5    | 14        | 22                             | 9                 | 40      |                               |          |      |

| WIZ4LZ 101Z03A | 2.7                       | 3.0  | 3.6  | 70        |                                | 3                 | 8       | 15                            | 9        | 40   |

### Notes:

- 2.Ball D3, H1, G2 and ball H6 for the FBGA package can be used to upgrade to a 4-Mbit, 8-Mbit, 16-Mbit and a 32-Mbit density, respectively.

- 3.NC "no connect"—not connected internally to the die.

- 4.DNU (Do Not Use) pins have to be left floating or tied to Vss to ensure proper application.

- 5. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at  $V_{CC} = V_{CC(typ.)}$ ,  $T_A = 25^{\circ}C$ .

Publication Date: Jul. 2008 Revision: 1.2 3/14

## **Maximum Ratings**

| Static Discharge Voltage       | >2001V   |

|--------------------------------|----------|

| (per MIL-STD-883, Method 3015) |          |

| Latch-up Current               | > 200 mA |

## **Operating Range**

| Range      | Ambient<br>Temperature(T <sub>A</sub> ) | V <sub>CC</sub> |

|------------|-----------------------------------------|-----------------|

| Extended   | -25°C to +85°C                          | 2.7V to 3.6V    |

| Industrial | -40°C to +85°C                          | 2.7V to 3.6V    |

**Electrical Characteristics (Over the Operating Range)**

|                  |                                              |                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                             |                          | -55         |                        |                          | -70         |                        |      |

|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------|-------------|------------------------|--------------------------|-------------|------------------------|------|

| Parameter        | Description                                  | Test Conditions                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               | Min.                     | Typ<br>.[5] | Max.                   | Min.                     | Typ.<br>[5] | Max.                   | Unit |

| Vcc              | Supply Voltage                               |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               | 2.7                      | 3.0         | 3.6                    | 2.7                      | 3.0         | 3.6                    | V    |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                       | I <sub>OH</sub> = −0.1 mA                                                                                                                                                                                                                                                                                                                                                                  | V <sub>CC</sub> = 2.70V                                                                       | V <sub>CC</sub> -<br>0.4 |             |                        | V <sub>CC</sub> -<br>0.4 |             |                        | V    |

| V <sub>OL</sub>  | Output LOW<br>Voltage                        | I <sub>OL</sub> = 0.1 mA                                                                                                                                                                                                                                                                                                                                                                   | V <sub>CC</sub> = 2.70V                                                                       |                          |             | 0.4                    |                          |             | 0.4                    | V    |

| V <sub>IH</sub>  | Input HIGH<br>Voltage                        | V <sub>CC</sub> = 2.7V t                                                                                                                                                                                                                                                                                                                                                                   | o 3.6V                                                                                        | 0.8*<br>V <sub>CC</sub>  |             | V <sub>CC</sub> + 0.4V | 0.8*<br>V <sub>CC</sub>  |             | V <sub>CC</sub> + 0.4V | V    |

| V <sub>IL</sub>  | Input LOW Voltage                            |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               |                          |             |                        | -0.4                     |             | 0.4                    | V    |

| I <sub>IX</sub>  | Input Leakage<br>Current                     | GND ≤V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                       | -1                                                                                            |                          | +1          | -1                     |                          | +1          | μΑ                     |      |

| l <sub>OZ</sub>  | Output Leakage<br>Current                    | $GND \leq V_{OUT} \leq V_{CC}$                                                                                                                                                                                                                                                                                                                                                             | Output Disabled                                                                               | -1                       |             | +1                     | -1                       |             | +1                     | μΑ   |

|                  | V <sub>CC</sub> Operating                    | $f = f_{MAX} = 1/t_{RC}$                                                                                                                                                                                                                                                                                                                                                                   | $V_{CC} = V_{CCmax}$                                                                          |                          | 14          | 22                     |                          | 8           | 15                     | mA   |

| I <sub>CC</sub>  | Supply Current                               | f = 1 MHz                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>OUT</sub> = 0mA<br>CMOS levels                                                         |                          | 1           | 5                      |                          | 1           | 5                      | mA   |

| I <sub>SB1</sub> | Automatic CE Power-Down Current —CMOS Inputs | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V}$ $\text{V}_{\text{IN}} \ge \text{V}_{\text{CC}} - 0.2\text{V},  \text{V}_{\text{IN}} \le 0.2\text{V},  \text{f} = \text{f}_{\text{MAX}}$ (Address and Data Only), $\text{f} = 0  (\overline{\text{OE}}, \overline{\text{WE}}, \overline{\text{BHE}} \text{ and } \overline{\text{BLE}}),  \text{V}_{\text{CC}} = 3.6\text{V}$ |                                                                                               |                          | 40          | 250                    |                          | 40          | 250                    | μΑ   |

| I <sub>SB2</sub> | Automatic CE Power-Down Current —CMOS Inputs | CE ≥V <sub>CC</sub> -0.2V                                                                                                                                                                                                                                                                                                                                                                  | $\overline{CE} \ge V_{CC} - 0.2V$<br>$V_{IN} \ge V_{CC} - 0.2V$ or $V_{IN} \le 0.2V$ , f = 0, |                          | 9           | 40                     |                          | 9           | 40                     | μΑ   |

Capacitance[9]

| - apacitarios [ | 7.1                |                        |      |      |

|-----------------|--------------------|------------------------|------|------|

| Parameter       | Description        | Test Conditions        | Max. | Unit |

| C <sub>IN</sub> | Input Capacitance  | TA = 25°C, f = 1 MHz   | 8    | pF   |

| Сопт            | Output Capacitance | $V_{CC} = V_{CC(typ)}$ | 8    | pF   |

Thermal Resistance[9]

| Parameter | Description                             | BGA                                                                                                           | Unit |      |

|-----------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|

| ΘЈΑ       | Thermal Resistance(Junction to Ambient) | Test conditions follow standard test methods and procedures for measuring thermal impedance, per EIA/ JESD51. | 55   | °C/W |

| ΘJC       | Thermal Resistance (Junction to Case)   |                                                                                                               | 17   | °C/W |

Notes:  $6.V_{IL(MIN)} = -0.5V$  for pulse durations less than 20 ns.

$7.V_{IH(Max)} = V_{CC} + 0.5V$  for pulse durations less than 20 ns.

8. Overshoot and undershoot specifications are characterized and are not 100% tested.

9. Tested initially and after any design or process changes that may affect these parameters.

Publication Date: Jul. 2008

Revision: 1.2 4/14

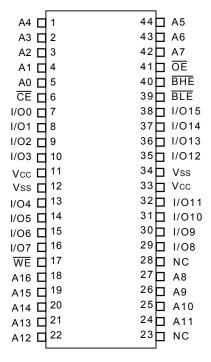

### **AC Test Loads and Waveforms**

| Parameters      | 3.0V V <sub>CC</sub> | Unit |

|-----------------|----------------------|------|

| R1              | 22000                | Ω    |

| R2              | 22000                | Ω    |

| R <sub>TH</sub> | 11000                | Ω    |

| $V_{TH}$        | 1.50                 | V    |

### **Switching Characteristics Over the Operating Range[10]**

| Parameter            | Description                    | -55 [1   | [4]  | -7   | 0    | Unit  |

|----------------------|--------------------------------|----------|------|------|------|-------|

| Parameter            | Description                    | Min.     | Max. | Min. | Max. | Offic |

| Read Cycle           |                                |          |      |      |      |       |

| t <sub>RC</sub>      | Read Cycle Time                | 55[14]   |      | 70   |      | ns    |

| t <sub>AA</sub>      | Address to Data Valid          |          | 55   |      | 70   | ns    |

| t <sub>OHA</sub>     | Data Hold from Address Change  | 5        |      | 10   |      | ns    |

| t <sub>ACE</sub>     | CE LOW to Data Valid           |          | 55   |      | 70   | ns    |

| t <sub>DOE</sub>     | OE LOW to Data Valid           |          | 25   |      | 35   | ns    |

| t <sub>LZOE</sub>    | OE LOW to LOW Z[11, 13]        | 5        |      | 5    |      | ns    |

| t <sub>HZOE</sub>    | OE HIGH to High Z[11, 13]      |          | 25   |      | 25   | ns    |

| tLZCE                | CE LOW to Low Z[11, 13]        | 2        |      | 5    |      | ns    |

| t <sub>HZCE</sub>    | CE HIGH to High Z[11, 13]      |          | 25   |      | 25   | ns    |

| t <sub>DBE</sub>     | BLE / BHE LOW to Data Valid    |          | 55   |      | 70   | ns    |

| t <sub>LZBE</sub>    | BLE / BHE LOW to Low Z[11, 13] | 5        |      | 5    |      | ns    |

| t <sub>HZBE</sub>    | BLE/BHE HIGH to HIGH Z[11, 13] |          | 10   |      | 25   | ns    |

| t <sub>SK</sub> [14] | Address Skew                   |          | 0    |      | 10   | ns    |

| Write Cycle[12]      |                                | <b>,</b> | ,    | 1    | 1    | 1     |

| t <sub>wc</sub>      | Write Cycle Time               | 55       |      | 70   |      | ns    |

| t <sub>SCE</sub>     | CE LOW to Write End            | 45       |      | 60   |      | ns    |

| t <sub>AW</sub>      | Address Set-Up to Write End    | 45       |      | 60   |      | ns    |

| t <sub>HA</sub>      | Address Hold from Write End    | 0        |      | 0    |      | ns    |

| t <sub>SA</sub>      | Address Set-Up to Write Start  | 0        |      | 0    |      | ns    |

| t <sub>PWE</sub>     | WE Pulse Width                 | 40       |      | 45   |      | ns    |

#### Notes:

- 10. Test conditions for all parameters other than tri-state parameters assume signal transition time of 1 ns/V, timing reference levels of  $V_{CC(typ)}/2$ , input pulse levels of 0V to  $V_{CC(typ.)}$ , and output loading of the specified  $I_{OL}/I_{OH}$  as shown in the "AC Test Loads and Waveforms" section.

- 11.  $t_{HZOE}$ ,  $t_{HZCE}$ ,  $t_{HZBE}$ , and  $t_{HZWE}$  transitions are measured when the outputs enter a high impedance state.12. The internal Write time of the memory is defined by the overlap of  $\overline{WE}$ ,  $\overline{CE} = V_{IL}$ ,  $\overline{BHE}$  and/or  $\overline{BLE} = V_{IL}$ . All signals must be ACTIVE to initiate a write and any of these signals can terminate a write by going INACTIVE. The data input set-up and hold timing should be referenced to the edge of the signal that terminates the write.

- 13. High-Z and Low-Z parameters are characterized and are not 100% tested.

- 14. To achieve 55-ns performance, the read access should be  $\overline{CE}$  controlled. In this case  $t_{ACE}$  is the critical parameter and  $t_{SK}$  is satisfied when the addresses are stable prior to chip enable going active. For the 70-ns cycle, the addresses must be stable within 10 ns after the start of the read cycle.

Publication Date: Jul. 2008 Revision: 1.2 5/14

## Switching Characteristics Over the Operating Range (continued)[10]

| Parameter         | Description              | -55 [1 | 4]        | -7 | Unit |    |

|-------------------|--------------------------|--------|-----------|----|------|----|

| Parameter         | Description              | Min.   | Min. Max. |    | Max. |    |

| $t_{BW}$          | BLE/BHE LOW to Write End | 50     |           | 60 |      | ns |

| $t_{SD}$          | Data Set-Up to Write End | 25     |           | 45 |      | ns |

| t <sub>HD</sub>   | Data Hold from Write End | 0      |           | 0  |      | ns |

| t <sub>HZWE</sub> | WE LOW to High-Z[11, 13] |        | 25        |    | 25   | ns |

| t <sub>LZWE</sub> | WE HIGH to Low-Z[11, 13] | 5      |           | 5  |      | ns |

## **Switching Waveforms**

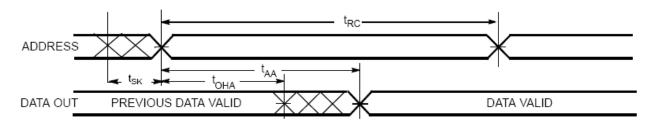

Read Cycle 1 (Address Transition Controlled)[15, 16, 17]

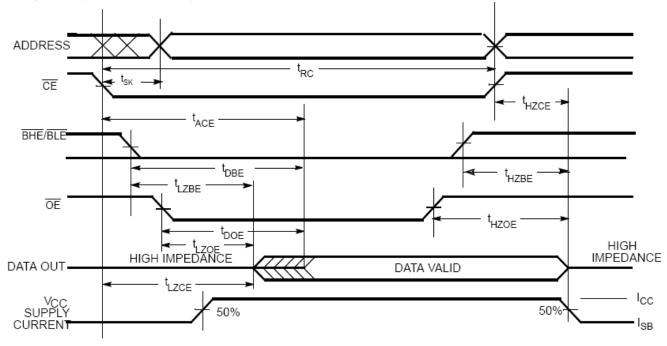

## Read Cycle 2 (OE Controlled)[16, 17]

### Notes:

- 15. Device is continuously selected.  $\overline{OE}$ ,  $\overline{CE} = V_{IL}$ .

- 16. WE is HIGH for Read Cycle.

- 17. For the 55-ns Cycle, the addresses must not toggle once the read is started on the device. For the 70-ns Cycle, the addresses must be stable within 10 ns after the start of the read cycle.

Publication Date: Jul. 2008 Revision: 1.2 6/14

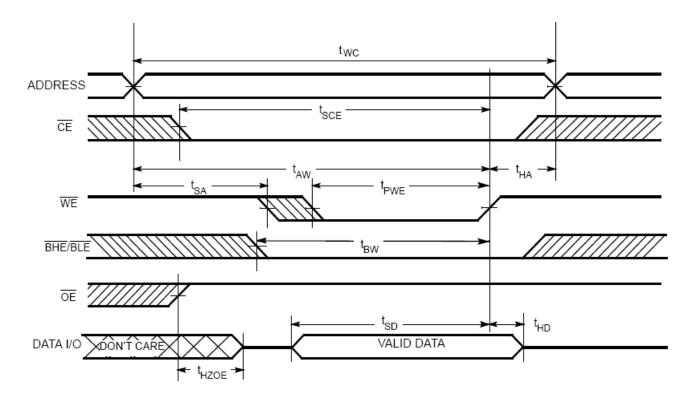

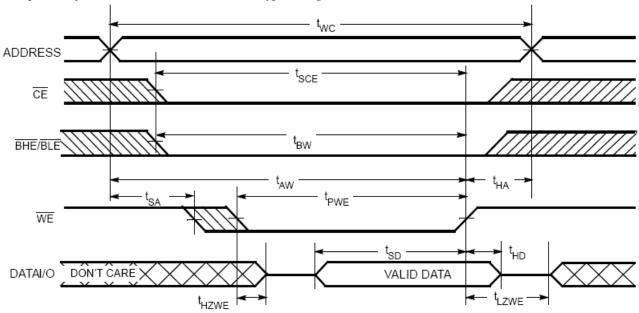

# Switching Waveforms (continued) Write Cycle 1 (WE Controlled)[12, 13, 18, 19, 20]

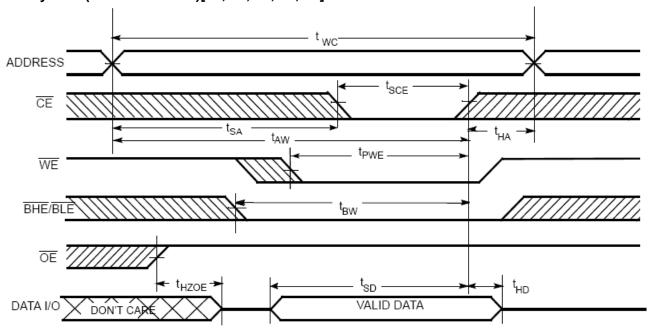

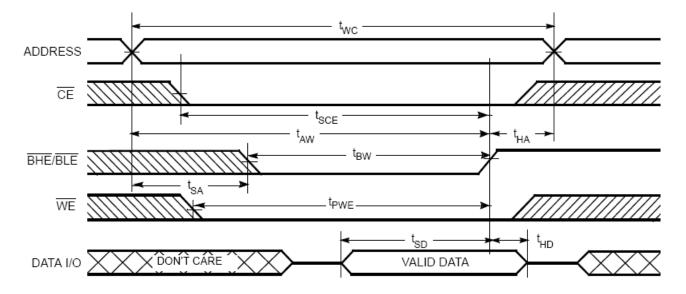

## Write Cycle 2 (CE Controlled)[12, 13, 18, 19, 20]

### Notes:

18.Data I/O is high impedance if  $\overline{OE} \ge V_{IH}$ .

19.If Chip Enable goes INACTIVE with  $\overline{\text{WE}}$  = V<sub>IH</sub>, the output remains in a high-impedance state.

20. During the DON'T CARE period in the DATA I/O waveform, the I/Os are in output state and input signals should not be applied.

## **Switching Waveforms (continued)**

## Write Cycle 3 (WE Controlled, OE LOW)[19, 20]

# Write Cycle 4 (BHE/BLE Controlled, OE LOW)[19, 20]

Revision: 1.2

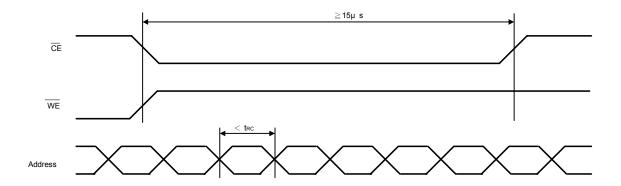

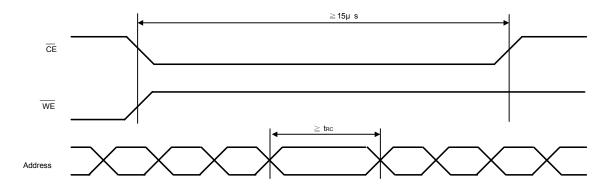

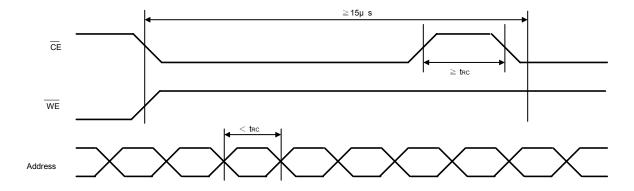

## **Avoid Timing**

ESMT Pseudo SRAM has a timing which is not supported at read operation, If your system has multiple invalid address signal shorter than t<sub>RC</sub> during over 15µs at read operation shown as in Abnormal Timing, it requires a normal read timing at leat during 15 $\mu$ s shown as in Avoidable timing 1 or toggle  $\overline{CE}$  to high ( $\geq t_{RC}$ ) one time at least shown as in Avoidable Timing 2.

## **Abnormal Timing**

## **Avoidable Timing 1**

## **Avoidable Timing 2**

Elite Semiconductor Memory Technology Inc.

Truth Table[21]

| CE | WE | ŌĒ | BHE | BLE | Inputs/Outputs                                                                                   | Mode                | Power                      |

|----|----|----|-----|-----|--------------------------------------------------------------------------------------------------|---------------------|----------------------------|

| Н  | Х  | Х  | Х   | Х   | High Z                                                                                           | Deselect/Power-Down | Standby (I <sub>SB</sub> ) |

| Х  | Х  | Х  | Н   | Н   | High Z                                                                                           | Deselect/Power-Down | Standby (I <sub>SB</sub> ) |

| L  | Н  | L  | L   | L   | Data Out (I/O <sub>0</sub> –I/O <sub>15</sub> )                                                  | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | L  | Н   | L   | Data Out (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>High Z (I/O <sub>8</sub> –I/O <sub>15</sub> ) | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | L  | L   | Н   | High Z (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>Data Out (I/O <sub>8</sub> –I/O <sub>15</sub> ) | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | L   | Н   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | Н   | L   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | L   | L   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | L   | L   | Data In (I/O <sub>0</sub> –I/O <sub>15</sub> )                                                   | Write               | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | Н   | L   | Data In (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>High Z (I/O <sub>8</sub> –I/O <sub>15</sub> )  | Write               | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | L   | Н   | High Z (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>Data In (I/O <sub>8</sub> –I/O <sub>15</sub> )  | Write               | Active (I <sub>CC</sub> )  |

Note

21.H = Logic HIGH, L = Logic LOW, X = Don't Care.

# **Ordering information**

| Speed(ns) | Ordering Code      | Package Type                                          | Operating Range |

|-----------|--------------------|-------------------------------------------------------|-----------------|

| 55        | M24L216128SA-55BEG | 48-ball Very Fine Pitch BGA (6.0x8.0x1.0mm) (Pb-free) | Extended        |

| 70        | M24L216128SA-70BEG | 48-ball Very Fine Pitch BGA (6.0x8.0x1.0mm) (Pb-free) | Extended        |

| 55        | M24L216128SA-55TEG | 44-pin TSOPII (Pb-free)                               | Extended        |

| 70        | M24L216128SA-70TEG | 44-pin TSOPII (Pb-free)                               | Extended        |

| 55        | M24L216128SA-55BIG | 48-ball Very Fine Pitch BGA (6.0x8.0x1.0mm) (Pb-free) | Industrial      |

| 70        | M24L216128SA-70BIG | 48-ball Very Fine Pitch BGA (6.0x8.0x1.0mm) (Pb-free) | Industrial      |

| 55        | M24L216128SA-55TIG | 44-pin TSOPII (Pb-free)                               | Industrial      |

| 70        | M24L216128SA-70TIG | 44-pin TSOPII (Pb-free)                               | Industrial      |

Publication Date: Jul. 2008 Revision: 1.2 10/14

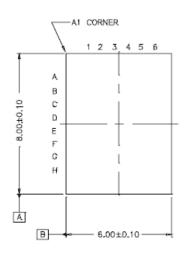

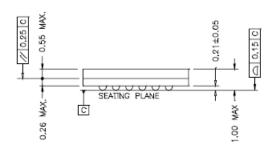

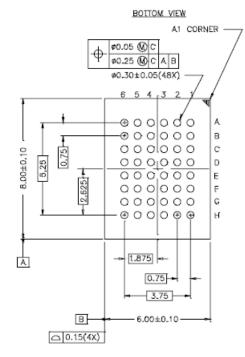

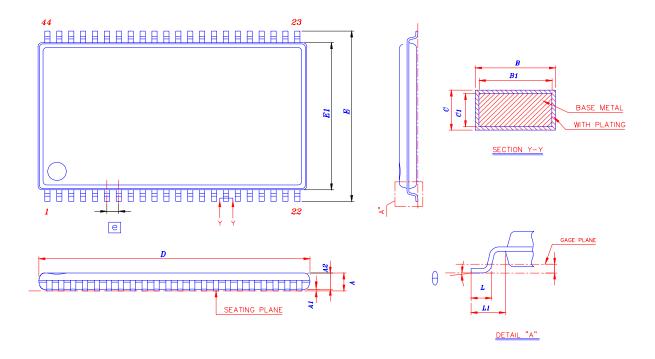

## **Package Diagram**

## 48-Lead VFBGA (6 x 8 x 1 mm)

51-85150-\*B

44-LEAD TSOP(II) PRAM(400mil)

| Symbol     | Di    | mension in n | nm         | Dimension in inch |            |            |  |

|------------|-------|--------------|------------|-------------------|------------|------------|--|

|            | Min   | Norm         | Max        | Min               | Norm       | Max        |  |

| Α          |       |              | 1.20       |                   |            | 0.047      |  |

| <b>A</b> 1 | 0.05  |              | 0.15       | 0.002             |            | 0.006      |  |

| A2         | 0.95  | 1.00         | 1.05       | 0.037             | 0.039      | 0.042      |  |

| В          | 0.30  |              | 0.45       | 0.012             |            | 0.018      |  |

| B1         | 0.30  | 0.35         | 0.40       | 0.012             | 0.014      | 0.016      |  |

| С          | 0.12  |              | 0.21       | 0.005             |            | 0.008      |  |

| C1         | 0.10  |              | 0.16       | 0.004             |            | 0.006      |  |

| D          | 18.28 | 18.41        | 18.54      | 0.720             | 0.725      | 0.730      |  |

| ZD         |       | 0.805 REF    |            |                   | 0.0317 REF | :          |  |

| E          | 11.56 | 11.76        | 11.96      | 0.455             | 0.463      | 0.471      |  |

| E1         | 10.03 | 10.16        | 10.29      | 0.395             | 0.400      | 0.4        |  |

| L          | 0.40  | 0.59         | 0.69       | 0.016             | 0.023      | 0.027      |  |

| L1         |       | 0.80 REF     |            | 0.031 REF         |            |            |  |

| е          |       | 0.80 BSC     |            | 0.0315 BSC        |            |            |  |

| θ          | 0°    |              | <b>8</b> ° | 0°                |            | <b>8</b> ° |  |

# **Revision History**

| Revision | Date       | Description                                                                                                |

|----------|------------|------------------------------------------------------------------------------------------------------------|

| 1.0      | 2007.05.11 | Original                                                                                                   |

| 1.1      | 2008.02.29 | Add 44-pin TSOPII package     Add Avoid timing                                                             |

| 1.2      | 2008.07.04 | Move Revision History to the last     Modify voltage range 2.7V~3.3V to 2.7V~3.6V     Add Industrial grade |

## **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Jul. 2008 Revision: 1.2 14/14